Karl-Hermann Cordes

Andreas Waag

Nicolas Heuck

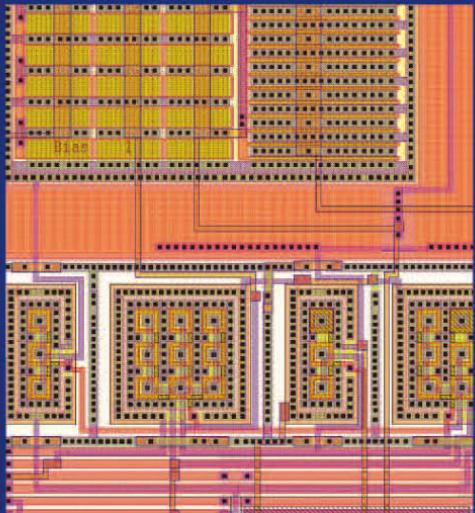

# Integrierte Schaltungen

Grundlagen – Prozesse – Design – Layout

## **Integrierte Schaltungen**

# **Integrierte Schaltungen**

## **Inhaltsverzeichnis**

Integrierte Schaltungen: Grundlagen Prozesse Design

Layout

### **Inhaltsverzeichnis**

#### **Vorwort**

#### **Teil I Grundlagen integrierter Schaltungen**

- 1 Technologien der Mikroelektronik

- 2 Physikalische Grundlagen der Halbleitertechnik

- 3 Integrierte Bauelemente

- 4 Technologie integrierter Schaltungen

- 5 Aufbau- und Verbindungstechnik integrierter Schaltungen

- 6 Defektmechanismen und Teststrategien

#### **Teil II Prozesse und Layout integrierter Schaltungen**

- 7 Standardprozesse der IC-Fertigung

- 8 Grundregeln für den Entwurf integrierter Schaltungen

#### **Teil III Analoge integrierte Schaltungen: Design, Simulation und Layout**

- 9 Stromspiegelschaltungen

- 10 Stromquellen

- 11 Spannungsreferenzen

- 12 Das Differenztransistorpaar

- 13 Operationsverstärker

- 14 Einführung in GM-C-Schaltungen

#### **Teil IV Digitale integrierte Schaltungen: Design, Simulation und Layout**

- 15 Grundlagen digitaler integrierter Schaltungen

- 16 Design und Layout digitaler Gatter in Emitter-gekoppelter Logik (ECL)

# Inhaltsverzeichnis

17 Design und Layout digitaler Gatter in Transistor-Transistor-Logik (TTL)

18 Design und Layout digitaler Gatter in CMOS

19 Neue Entwicklungen

Anhang A

Register

## Vorwort

Inhalt

Zielgruppe

Danksagung

Webseite

## Teil I Grundlagen integrierter Schaltungen

### 1 Technologien der Mikroelektronik

1.1 Leiterplattentechnik

1.2 Hybridtechnik

1.3 Halbleitertechnik

1.3.1 Integrierte Schaltungen

1.3.2 Aufbau einer integrierten Schaltung

1.3.3 Entwurfsprozess integrierter Schaltungen

### 2 Physikalische Grundlagen der Halbleitertechnik

2.1 Grundlagen der Halbleiterphysik

2.2 Vom einzelnen Quantentrog zur Bandstruktur von Halbleitern

2.2.1 Der Formalismus der Quantenmechanik

2.2.2 Bindungen und Austauschwechselwirkung

2.2.3 Der Spin des Elektrons

2.2.4 Die Entstehung von Bändern

2.3 Bandstruktur und Ladungsträgertransport

2.3.1 Fermi-Energie und die Ladungsträgerkonzentration

2.3.2 Akzeptoren und Donatoren

2.3.3 Driftstrom und Diffusionsstrom

2.4 Eigenschaften von Silizium

### 3 Integrierte Bauelemente

# Inhaltsverzeichnis

- 3.1 Der PN-Übergang

- 3.2 Der Bipolar-Transistor

- 3.3 Der Junction-FET (JFET)

- 3.4 Der MOSFET

- 3.5 Passive Bauelemente

- 3.6 Kurzkanaleffekte und Skalierung

- 3.7 Geschwindigkeit eines MOSETs: Optimierung der Taktfrequenzen

- 3.8 MOS-Speicher.

- 3.1 Der PN-Übergang

- 3.1.1 3.1.1 Aufbau Aufbau und und Funktionsweise Funktionsweise

- 3.1.2 3.1.2 Der Der PN-PN-Übergang Übergang im im stromlosen stromlosen Zustand Zustand

- 3.1.3 3.1.3 Der Der PN-PN-Übergang Übergang mit mit äußerer äußerer Spannung Spannung

- 3.1.4 3.1.4 Die Die Kapazität Kapazität eines eines PN-PN-Übergangs Übergangs

- 3.1.5 3.1.5 Durchbruchspannung Durchbruchspannung einer einer Diode Diode

- 3.1.6 3.1.6 Einfluss Einfluss der der Rekombination Rekombination

- 3.2 3.2 Der Der Bipolar-Bipolar-Transistor Transistor

- 3.2.1 3.2.1 Funktionsweise Funktionsweise des des Bipolar-Bipolar-Transistors Transistors

- 3.2.2 3.2.2 Beschaltung Beschaltung eines eines Bipolar-Bipolar-Transistors Transistors

- 3.2.3 3.2.3 Kleinsignalgrößen Kleinsignalgrößen

- 3.2.4 3.2.4 Kleinsignal-Kleinsignal-Ersatzschaltbild Ersatzschaltbild

- 3.2.5 3.2.5 Aufbau Aufbau eines eines integrierten integrierten Bipolar-Bipolar-Transistors Transistors

- 3.2.6 3.2.6 Temperaturabhängigkeiten Temperaturabhängigkeiten von von Transistorparametern Transistorparametern

- 3.2.7 3.2.7 Frequenzverhalten Frequenzverhalten von von Bipolar-Bipolar-Transistoren Transistoren

- 3.2.8 3.2.8 Transistorschaltbild Transistorschaltbild

- 3.2.9 3.2.9 Ersatzschaltbild Ersatzschaltbild und und SPICE-SPICE-Parameter Parameter des des Bipolar-Bipolar-Transistors Transistors

- 3.3 3.3 Der Der Junction-Junction-FET FET ((JFET) JFET)

- 3.3.1 3.3.1 Funktionsweise Funktionsweise

# Inhaltsverzeichnis

- 3.3.2 3.3.2 Kennliniengleichung Kennliniengleichung

- 3.3.3 3.3.3 Aufbau Aufbau eines eines integrierten integrierten JFETs JFETs

- 3.3.4 3.3.4 Kleinsignalgrößen Kleinsignalgrößen

- 3.3.5 3.3.5 Symbole Symbole des des JFETs JFETs

- 3.3.6 3.3.6 Frequenzverhalten Frequenzverhalten

- 3.3.7 3.3.7 Ersatzschaltbild Ersatzschaltbild und und SPICE-SPICE-Parameter

Parameter des des JFETs JFETs

- 3.4 3.4 Der Der MOSFET MOSFET**

- 3.4.1 3.4.1 Aufbau Aufbau und und Funktionsweise Funktionsweise

- 3.4.2 3.4.2 Kennlinien Kennlinien eines eines MOSFETs MOSFETs

- 3.4.3 3.4.3 Weitere Weitere MOSFET-MOSFET-Typen Typen und und ihre ihre

Schaltungssymbole Schaltungssymbole

- 3.4.4 3.4.4 CMOS-CMOS-Transistorpaar Transistorpaar

- 3.4.5 3.4.5 Kleinsignalgrößen Kleinsignalgrößen

- 3.4.6 3.4.6 Temperaturverhalten Temperaturverhalten

- 3.4.7 3.4.7 Ersatzschaltbild Ersatzschaltbild und und SPICE-SPICE-Parameter

Parameter des des MOSFETs MOSFETs

- 3.5 3.5 Passive Bauelemente Bauelemente**

- 3.5.1 3.5.1 Widerstände Widerstände

- 3.5.2 3.5.2 Kondensatoren Kondensatoren

- 3.6 3.6 Kurzkanaleffekte Kurzkanaleffekte und und Skalierung

Skalierung**

- 3.7 3.7 Geschwindigkeit Geschwindigkeit eines eines MOSETs: MOSETs:

Optimierung Optimierung der der Taktfrequenzen Taktfrequenzen**

- 3.8 3.8 MOS-MOS-Speicher Speicher**

- 3.8.1 3.8.1 Dynamic Dynamic Random Random Access Access Memories Memories ((DRAM)

DRAM)

- 3.8.2 3.8.2 Static Static Random Random Access Access Memories Memories ((SRAM)

SRAM)

- 3.8.3 3.8.3 Floating-Floating-Gate-Gate-Speicher Speicher

- 4 Technologie integrierter Schaltungen**

- 4.1 Wafer-Herstellung

- 4.2 Lithografie und Reinraumtechnik

- 4.3 Dotierung.

# Inhaltsverzeichnis

4.4 Schichttechnik

4.5 Ätztechnik

4.6 Metallisierung, Planarisierung und Durchkontaktierung in integrierten

Schaltungen

4.1 4.1 Wafer-Wafer-Herstellung Herstellung

4.1.1 4.1.1 Klassische Klassische Silizium-Silizium-Technologie Technologie

4.1.2 4.1.2 SOI SOI Silicon Silicon On On Insulator Insulator

4.2 4.2 Lithografie Lithografie und und Reinraumtechnik

Reinraumtechnik

4.2.1 4.2.1 Fotoresist Fotoresist

4.2.2 4.2.2 Maskentechnik Maskentechnik und und Belichtung Belichtung

4.2.3 4.2.3 ReinräumeReinräume

4.3 4.3 Dotierung Dotierung

4.3.1 4.3.1 Ionenimplantation Ionenimplantation

4.3.2 4.3.2 Diffusion Diffusion

4.4 4.4 Schichttechnik Schichttechnik

4.4.1 4.4.1 Sputtern Sputtern

4.4.2 4.4.2 CVD-CVD-Verfahren Verfahren

4.4.3 4.4.3 Aufdampfverfahren Aufdampfverfahren

4.4.4 4.4.4 Thermische Thermische Oxidation Oxidation

4.4.5 4.4.5 Silizierung Silizierung

4.5 4.5 Ätztechnik Ätztechnik

4.5.1 4.5.1 Nassätzen Nassätzen

4.5.2 4.5.2 Trockenätzen Trockenätzen

4.6 4.6 Metallisierung, Metallisierung, Planarisierung Planarisierung und und

Durchkontaktierung Durchkontaktierung in in integrierten integrierten Schaltungen

Schaltungen

4.6.1 4.6.1 Leiterbahnen Leiterbahnen

4.6.2 4.6.2 Planarisierung Planarisierung

4.6.3 4.6.3 Kontakte Kontakte und und Vias Vias

5 Aufbau- und Verbindungstechnik integrierter Schaltungen

5.1 Vom Front-End zum Back-End.

5.2 Kontaktierung und Befestigung integrierter Schaltungen

# Inhaltsverzeichnis

- 5.3 Single-Chip-Packaging

- 5.4 Direktmontage: Chip-On-Board

- 5.5 Multi-Chip-Packaging

- 5.1 5.1 Vom Vom Front-Front-End End zum zum Back-Back-End End

- 5.2 5.2 Kontaktierung Kontaktierung und und Befestigung Befestigung

- integrierter integrierter Schaltungen Schaltungen

- 5.2.1 5.2.1 Drahtbunden: Drahtbunden: Chip-Chip-and-and-Wire Wire

- 5.2.2 5.2.2 Flip-Flip-Chip-Chip-Kontaktierung Kontaktierung

- 5.2.3 5.2.3 Tape-Tape-Automated-Automated-Bonding Bonding

- 5.2.4 5.2.4 Chipbefestigung Chipbefestigung

- 5.3 5.3 Single-Single-Chip-Chip-Packaging Packaging

- 5.3.1 5.3.1 Packages Packages für für die die THT-THT-Montage: Montage: DIP, DIP, SIP SIP und und PGA PGA

- 5.3.2 5.3.2 Packages Packages für für die die SMT-SMT-Montage: Montage: SOP, SOP, QFP QFP und und BGA BGA

- 5.3.3 5.3.3 Eigenschaften Eigenschaften von von Vergussmasse Vergussmasse und und Lead-Lead-Frame Frame in in Kunststoffgehäusen Kunststoffgehäusen

- 5.4 5.4 Direktmontage: Direktmontage: Chip-Chip-On-On-Board Board

- 5.5 5.5 Multi-Multi-Chip-Chip-Packaging Packaging

## 6 Defektmechanismen und Teststrategien

- 6.1 Ausfallmechanismen und Defekte in integrierten Schaltungen

- 6.2 Teststrategien für integrierte Schaltungen

- 6.3 Test digitaler Schaltungen

- 6.4 Test analoger Schaltungen

- 6.5 Test eines analogen ASICs

- 6.1 6.1 Ausfallmechanismen Ausfallmechanismen und und Defekte Defekte in in integrierten integrierten Schaltungen Schaltungen

- 6.2 6.2 Teststrategien Teststrategien für für integrierte integrierte Schaltungen Schaltungen

- 6.2.1 6.2.1 Funktionaler Funktionaler Test Test

- 6.2.2 6.2.2 Struktureller Struktureller Test Test

- 6.2.3 6.2.3 Testabläufe Testabläufe

# Inhaltsverzeichnis

- 6.3 6.3 Test digitaler Schaltungen

- 6.3.1 6.3.1 Fehlermodelle und Testmustererzeugung

- Testmustererzeugung

- 6.3.2 6.3.2 Testfreundlicher Entwurf digitaler ICs

- Testfreundlicher Entwurf

- 6.4 6.4 Test analoger Schaltungen

- 6.5 6.5 Test eines analogen ASICs

- 6.5.1 6.5.1 Testaufbauten und Electrical Test Specification ((ETSI) ETS)

- Testaufbauten

- Electrical Test

- Specification

- ((ETSI) ETS)

- 6.5.2 6.5.2 Testprozedur

- Testprozedur

## Teil II Prozesse und Layout integrierter Schaltungen

### 7 Standardprozesse der IC-Fertigung

- 7.1 Layer und Masken

- 7.2 Prozessanbieter und Prozesse ein Überblick

- 7.3 Bipolar-Prozesse

- 7.3.1 Standard-Bipolar-Prozess (C36)

- 7.3.2 Erweiterter Bipolar-Prozess (C14)

- 7.3.3 Widerstände in Bipolar-Prozessen

- 7.3.4 Kondensatoren in Bipolar-Prozessen

### 7.4 CMOS-Prozesse

- 7.4.1 CMOS-Standardprozess (CM5)

- 7.4.2 Fortschrittliche CMOS-Prozesse

- 7.4.3 Widerstände in CMOS-Prozessen

- 7.4.4 Kondensatoren in CMOS-Prozessen

### 7.5 Bipolar-CMOS-Technologien

## 8 Grundregeln für den Entwurf integrierter Schaltungen

- 8.1 Kurze Einführung in die Schaltungsberechnung

- 8.1.1 Aufgabenstellung (Spezifikation)

- 8.1.2 Kurze Erklärung der Schaltung

- 8.1.3 Lösung (Grobdimensionierung)

- 8.2 Hinweise zur Dimensionierung integrierter Schaltungen

- 8.2.1 Geometrische Abmessungen Passiver Elemente

- 8.2.2 Geometrische Abmessungen Aktiver Elemente

- 8.2.3 Absichern der Spezifikation durch eine Monte-Carlo-Simulation

# Inhaltsverzeichnis

## 8.3 Design-Rules

- 8.3.1 Abgeleitete Layer

- 8.3.2 Abstände und Weiten eines Prozess-Layers

- 8.3.3 Abstände zwischen verschiedenen Layern

- 8.3.4 Vergrößern und Verringern von Design-Maßen

- 8.3.5 Implementierung der Rules in das Layout-Programm

## 8.4 Layout-Synthese

- 8.4.1 Beispiel 1: Bipolar-Transistor

- 8.4.2 Beispiel 2: CMOS-Inverter

## 8.5 Richtlinien zur Layout-Erstellung

- 8.5.1 Paarung von Bauelementen (Matching)

- 8.5.2 Zusammenstellung wichtiger Layout-Regeln und Layout-Beispiele

- 8.5.3 Hinweise für Zellen einer Bibliothek

- 8.5.4 Spezielle Hinweise für CMOS-Zellen einer Bibliothek

- 8.5.5 Verbindungsleitungen

## 8.6 Parasitäre Effekte

- 8.6.1 Unerwünschte Kanalbildung, Vermeidung durch Channel-Stopper

- 8.6.2 Latch-Up in integrierten Schaltungen

## 8.7 Layout-Verifikation

- 8.7.1 Design-Rule-Check

- 8.7.2 Layout-Versus-Schematic (LVS)

## Teil III Analoge integrierte Schaltungen: Design, Simulation und Layout

## 9 Stromspiegelschaltungen

- 9.1 Der einfache Stromspiegel

- 9.2 Die Widlar-Schaltung

- 9.3 Widerstandsbestimmter Stromteiler

- 9.4 Korrektur von Stromspiegelfehlern

- 9.4.1 Korrektur des Basis-Strom-Einflusses

- 9.4.2 Kompensation des Early-Effekt-Einflusses

- 9.4.3 Korrektur von Offset-Fehlern

- 9.4.4 Reduzieren der Sättigungsspannung

- 9.4.5 Stromspiegel mit geregelter Kaskoden-Schaltung

# Inhaltsverzeichnis

## 9.5 Praktisches Beispiel

- 9.5.1 Aufgabenstellung

- 9.5.2 Lösung

- 9.5.3 Überprüfung des Ergebnisses und erste Korrektur

- 9.5.4 Zweite Korrektur

- 9.5.5 Layout-Erstellung

## 9.6 Dynamisches Verhalten von Stromspiegelschaltungen

- 9.6.1 Bipolare Stromspiegel

- 9.6.2 MOS-Stromspiegel

# 10 Stromquellen

## 10.1 Stromeinstellung über einen Widerstand

## 10.2 Stromquelle mit Vorwärtsregelung

## 10.3 Stromquelle mit einem JFET

## 10.4 Verwendung von UBE als Referenzspannung

## 10.5 PTAT-Stromquellen

- 10.5.1 Einfache PTAT-Stromquelle

- 10.5.2 PTAT-Stromquelle mit Early-Effekt-Kompensation nach Wilson

- 10.5.3 PTAT-Stromquelle mit Vorwärtsregelung

- 10.5.4 PTAT-mit mit Vorwärtsregelung und Kaskode

- 10.5.5 Erdi-Stromquelle

## 10.6 CMOS-Stromquellen

- 10.6.1 Beta-Multiplier

- 10.6.2 Praktisches Beispiel: Beta-Multiplier für kleine Ströme

- 10.6.3 CMOS-Stromquelle ohne Verwendung von Widerständen

## 10.7 Eine fast genaue Stromquelle

# 11 Spannungsreferenzen

## 11.1 Z-Diode als Spannungsreferenz

## 11.2 PTAT-Spannungsreferenzen

- 11.2.1 Einfache PTAT-Spannungsreferenz

- 11.2.2 Verwendung einer unsymmetrischen Differenzstufe

## 11.3 Bandgap-Spannungsreferenzen

- 11.3.1 Das Prinzip der Bandgap-Referenz

- 11.3.2 Die einfache Widlar-Bandgap-Referenz

# Inhaltsverzeichnis

- 11.3.3 Brokaw-Bandgap-Referenz

- 11.3.4 Widlar-Bandgap-Referenz

- 11.3.5 Beispiel: Design einer Widlar-Bandgap-Referenz

- 11.3.6 Second-Order-Temperaturkompensation

- 11.3.7 Zweipolare Vier-Transistor-Bandgap-Referenz

- 11.3.8 Referenzspannungen kleiner als 1 V

- 11.3.9 Bandgap-Referenzen in CMOS-Prozessen

## 12 Das Differenztransistorpaar

- 12.1 Das Emitter-gekoppelte Bipolar-Transistorpaar

- 12.1.1 Linearisierung durch Stromgegenkopplung

- 12.2 Das Source-gekoppelte MOSFET-Transistorpaar

## 13 Operationsverstärker

- 13.1 Allgemeines

- 13.2 Differenzeingangsstufe

- 13.2.1 Der Differenzverstärker

- 13.2.2 Eingangsstufe mit Widerständen

- 13.2.3 Differenzstufe mit Stromspiegelausgang

- 13.2.4 Eingangsstufe für Gleichtaktanteile außerhalb der Versorgungsspannung

- 13.2.5 PNP-Eingangsstufe

- 13.2.6 Kaskoden-Eingangsstufe mit Super-B-Transistoren

- 13.2.7 Kompensation des Eingangstromes

- 13.2.8 Präzisionseingangsschaltung

- 13.2.9 Rail-to-Rail-Eingangsschaltung

- 13.3 Eingangs-Offset

- 13.3.1 Bipolarer Eingang

- 13.3.2 MOS-Eingang

- 13.3.3 Offset-Trimmen

- 13.4 Ausgangsstufe

- 13.4.1 Emitter- bzw. Source-Folger-Ausgang

- 13.4.2 Komplementär-Ausgangsstufe im AB-Betrieb

- 13.4.3 CMOS-Push-Pull-Ausgangsstufe mit Inverter-Ansteuerung

- 13.4.4 Push-Pull-Ansteuerung über Fehlerverstärker

- 13.4.5 Einfacher Buffer im Gegentakt-A-Betrieb

- 13.5 Dynamisches Verhalten und Stabilität von Operationsverstärkern

# Inhaltsverzeichnis

13.5.1 Frequenzgang, Übertragungsfunktion

13.5.2 Stabilität eines gegengekoppelten Systems

13.5.3 Frequenzgangkorrektur

13.5.4 Miller-Korrektur des Frequenzganges

13.5.5 Slew-Rate

## 13.6 Design-Beispiele von Operationsverstärkern

13.6.1 Einfacher Bipolar-Operationsverstärker mit PNP-Eingang

13.6.2 Einfacher Operationsverstärker in CMOS

13.6.3 Einfacher Transconductance-Verstärker (OTA) in CMOS

## 13.7 Operationsverstärker mit symmetrischem Ausgang

## 13.8 Komplettes Design eines CMOS-Operationsverstärkers: Berechnung, Simulation, Korrektur und Layout

13.8.1 Zusammenstellung der Formeln

13.8.2 Aufgabenstellung

13.8.3 Berechnung der Schaltung

13.8.4 Simulationsergebnisse

13.8.5 Layout-Erstellung

13.8.6 Layout-Verifikation

## 14 Einführung in GM-C-Schaltungen

### 14.1 Grundschatungen

### 14.2 GM-C-Oszillatoren und GM-C-Filterschaltungen

14.2.1 GM-C-Oszillatoren

14.2.2 GM-C-Bandpass- und Tiefpass-Filter

### 14.3 Ausführung von GM-Zellen

## Teil IV Digitale integrierte Schaltungen: Design, Simulation und Layout

## 15 Grundlagen digitaler integrierter Schaltungen

### 15.1 Grundbegriffe der digitalen Schaltungstechnik

### 15.2 Digitaltechnik

### 15.3 Digitale Schaltungsfamilien

## 16 Design und Layout digitaler Gatter in Emitter-gekoppelter Logik (ECL)

# Inhaltsverzeichnis

## 16.1 Typisches NOR-OR-Gatter

- 16.1.1 Dimensionierung

- 16.1.2 Referenzspannung

- 16.1.3 Anschluss externer Geräte über Leitungen

- 16.1.4 Layout

- 16.1.5 Layout-Verifikation

## 16.2 ECL-Gatter mit reduzierter Verlustleistung

## 16.3 EECL-Gatter mit geringer Verlustleistung

- 16.3.1 Layout

- 16.3.2 Layout-Verifikation

## 16.4 Andere ECL-Gatter

# 17 Design und Layout digitaler Gatter in Transistor-Transistor-Logik (TTL)

- 17.1 Die NAND-Funktion und der Multi-Emitter-Eingang

- 17.2 Layout

- 17.3 Weitere Vereinfachungen

- 17.4 Verbesserung einiger Eigenschaften

# 18 Design und Layout digitaler Gatter in CMOS

## 18.1 Der CMOS-Inverter als grundlegendes Schaltungselement

- 18.1.1 Schaltpunkt

- 18.1.2 Statischer Querstrom

- 18.1.3 Transiente Verlustleistung

- 18.1.4 Dynamische Verlustleistung

- 18.1.5 Gesamte Verlustleistung

- 18.1.6 Zeitverhalten

- 18.1.7 Festlegung der geometrischen Abmessungen

- 18.1.8 Inverter-Layout

- 18.1.9 Inverter mit höherer Treiberfähigkeit

- 18.1.10 CMOS-Inverter mit kontrolliertem Querstrom

## 18.2 CMOS-Schmitt-Trigger

## 18.3 TTL-CMOS-Interface

## 18.4 Transfer- oder Transmission-Gate

## 18.5 Inverter mit Tri-State-Ausgang

# Inhaltsverzeichnis

- 18.6 Das Exklusiv-ODER-Gatter (XOR)

- 18.7 NAND- und NOR-Gatter

- 18.7.1 Layout

- 18.7.2 Zeitverhalten

- 18.8 Verallgemeinerte CMOS-Gate-Strukturen

- 18.8.1 Dimensionierung

- 18.8.2 Layout der AOI-Schaltungen

- 18.8.3 Abstrahieren des Schaltplanes durch Zweige anstelle der Transistoren

- 18.9 Pseudo-NMOS-Logik

- 18.10 Dynamische logische Schaltungen (C2MOS)

- 18.11 Domino-CMOS-Logik

- 18.12 Latches und Flip-Flops

- 18.12.1 Das einfache Latch und das RS-Flip-Flop

- 18.12.2 Getaktetes RS-Flip-Flop

- 18.12.3 Latch als Speicherzelle

- 18.12.4 Einfaches Daten-Flip-Flop (D-Flip-Flop)

- 18.12.5 Flanken-getriggertes D-Flip-Flop

- 18.12.6 Flanken-getriggertes D-Flip-Flop mit Set- und Reset-Eingang

## 19 Neue Entwicklungen

- 19.1 More than Moore

- 19.2 Verspanntes Silizium

- 19.3 Low-k- und High-k-Oxide als Dielektrika

- 19.4 Silizium-Photonik

- 19.5 Nano-FETs

- 19.6 Tri-Gate-Transistoren

- 19.7 Speichertechnologien

## Anhang A

- A.1 Frequenzgang eines einstufigen Verstärkers

- A.2 Simulation mit SPICE

## Register

Numerisch

Pearson

## **Inhaltsverzeichnis**

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

R

S

T

U

V

W

X

Z

Ins Internet: Weitere Infos zum Buch, Downloads, etc.

Copyright

## **Inhaltsverzeichnis**

## Copyright

Daten, Texte, Design und Grafiken dieses eBooks, sowie die eventuell angebotenen eBook-Zusatzdaten sind urheberrechtlich geschützt. Dieses eBook stellen wir lediglich als persönliche Einzelplatz-Lizenz zur Verfügung!

Jede andere Verwendung dieses eBooks oder zugehöriger Materialien und Informationen, einschliesslich

- der Reproduktion,

- der Weitergabe,

- des Weitervertriebs,

- der Platzierung im Internet,

in Intranets, in Extranets,

- der Veränderung,

- des Weiterverkaufs

- und der Veröffentlichung

bedarf der schriftlichen Genehmigung des Verlags.

Insbesondere ist die Entfernung oder Änderung des vom Verlag vergebenen Passwortschutzes ausdrücklich untersagt!

Bei Fragen zu diesem Thema wenden Sie sich bitte an: [info@pearson.de](mailto:info@pearson.de)

## Zusatzdaten

Möglicherweise liegt dem gedruckten Buch eine CD-ROM mit Zusatzdaten bei. Die Zurverfügungstellung dieser Daten auf unseren Websites ist eine freiwillige Leistung des Verlags. Der Rechtsweg ist ausgeschlossen.

## Hinweis

Dieses und viele weitere eBooks können Sie rund um die Uhr und legal auf unserer Website

herunterladen